Applied Materials Unveils Chip Wiring Innovations for More Energy-Efficient Computing

Applied Materials Unveils Chip Wiring Innovations for More Energy-Efficient Computing

- Industry's first use of ruthenium in high-volume production enables copper chip wiring to be scaled to the 2nm node and beyond and reduces resistance by as much as 25%

- New enhanced low-k dielectric material reduces chip capacitance and strengthens logic and DRAM chips for 3D stacking

- 業界首次使用釕在高容量生產中,使銅芯片佈線能夠擴展到2納米節點及更高,並將電阻降低高達25%。

- 新增強低介電材料可減少芯片電容和加強邏輯和DRAM芯片的三維堆疊

SANTA CLARA, Calif., July 08, 2024 (GLOBE NEWSWIRE) -- Applied Materials, Inc. today introduced materials engineering innovations designed to increase the performance-per-watt of computer systems by enabling copper wiring to scale to the 2nm logic node and beyond.

美國加利福尼亞州聖塔克拉拉,2024年7月8日(環球社交媒體公司)- 應用材料公司今天推出了材料工程創新,旨在通過使銅線縮放到2納米邏輯節點及更高,從而提高計算機系統的性能 - 每瓦功率。

"The AI era needs more energy-efficient computing, and chip wiring and stacking are critical to performance and power consumption," said Dr. Prabu Raja, President of the Semiconductor Products Group at Applied Materials. "Applied's newest integrated materials solution enables the industry to scale low-resistance copper wiring to the emerging angstrom nodes, while our latest low-k dielectric material simultaneously reduces capacitance and strengthens chips to take 3D stacking to new heights."

“AI 時代需要更節能的計算,而芯片佈線和堆疊對性能和能耗至關重要,”應用材料半導體產品組總裁Dr. Prabu Raja表示:“應用的最新集成材料解決方案使行業能夠將低電阻銅線擴展到新興的阿茲特克節點,而我們最新的低介電材料則可同時減少電容並增強芯片,將3D堆疊推向新的高度。”

Overcoming the Physics Challenges of Classic Moore's Law Scaling

克服傳統摩爾定律縮放的物理挑戰

Today's most advanced logic chips can contain tens of billions of transistors connected by more than 60 miles of microscopic copper wiring. Each layer of a chip's wiring begins with a thin film of dielectric material, which is etched to create channels that are filled with copper. Low-k dielectrics and copper have been the industry's workhorse wiring combination for decades, allowing chipmakers to deliver improvements in scaling, performance and power-efficiency with each generation.

如今,最先進的邏輯芯片可以包含數百億個晶體管,這些晶體管通過60英里以上的微小銅線相連接。芯片每一層的佈線都始於薄膜介電材料,該材料被刻蝕以創建通道,這些通道被填充有銅。低k介電材料和銅是行業的支柱佈線組合數十年,使芯片製造商能夠在每一代中提供縮放、性能和功率效率的改進。

However, as the industry scales to 2nm and below, thinner dielectric material renders chips mechanically weaker, and narrowing the copper wires creates steep increases in electrical resistance that can reduce chip performance and increase power consumption.

然而,隨着行業縮放到2納米及以下,更薄的介電材料使芯片在力學上更加脆弱,而縮小銅線會導致電阻急劇增加,這可能會降低芯片性能並增加能耗。

Enhanced Low-k Dielectric Reduces Interconnect Resistance and Strengthens Chips for 3D Stacking

增強的低介電材料可減少互連電阻並加強三維堆疊芯片

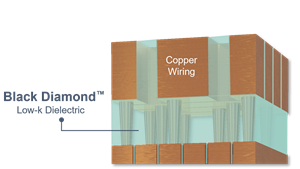

Applied's Black Diamond material has led the industry for decades, surrounding copper wires with a low-dielectric-constant – or "k-value" – film engineered to reduce the buildup of electrical charges that increase power consumption and cause interference between electrical signals.

多年來,Applied的黑鑽石材料一直領導着行業,在銅線周圍進行低介電常數-或“k值”-薄膜的包圍,該薄膜被設計用於減少電荷的積聚,從而增加功耗並在電信號之間造成干擾。

Applied today introduced an enhanced version of Black Diamond, the latest in the company's Producer Black Diamond PECVD* family. This new material reduces the minimum k-value to enable scaling to 2nm and below, while offering increased mechanical strength which is becoming critical as chipmakers and systems companies take 3D logic and memory stacking to new heights.

Applied今天推出了Black Diamond的增強版本,這是公司黑鑽石生產線的最新產品。這種新材料可降低最小k值,使其可擴展到2納米及以下,並提供了越來越關鍵的機械強度,因爲芯片製造商和系統公司將三維邏輯和存儲堆疊推向新的高度。

The latest Black Diamond technology is being adopted by all leading logic and DRAM chipmakers.

領先的邏輯和DRAm芯片製造商正在採用最新的Black Diamond技術。

New Binary Metal Liner Enables Ultrathin Copper Wires

新的二元金屬襯底可實現特薄銅導線

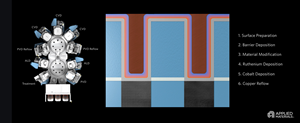

To scale chip wiring, chipmakers etch each layer of low-k film to create trenches, then deposit a barrier layer that prevents copper from migrating into the chip and creating yield issues. The barrier is then coated with a liner that ensures adhesion during the final copper reflow deposition sequence, which slowly fills the remaining volume with copper.

爲了擴展芯片佈線,芯片製造商會刻蝕低k膜的每一層以創建溝槽,然後塗一層屏障層,以防銅遷移到芯片中並造成產量問題。然後在屏障上塗覆一層襯底,以確保在最終的銅再流入沉積序列期間具有黏附性,該序列慢慢用銅填充剩餘體積。

As chipmakers further scale the wiring, the barrier and liner take up a larger percentage of the volume intended for wiring, and it becomes physically impossible to create low-resistance, void-free copper wiring in the remaining space.

隨着芯片製造商進一步縮放佈線,屏障和襯底佔用了剩餘空間的較大比例,無法在剩餘空間中創建低電阻的無瑕銅導線,這在物理上變得不可能。

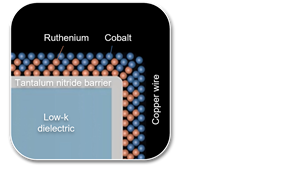

Today, Applied Materials publicly introduced its latest IMS (Integrated Materials Solution) which combines six different technologies in one high-vacuum system, including an industry-first combination of materials that enables chipmakers to scale copper wiring to the 2nm node and beyond. The solution is a binary metal combination of ruthenium and cobalt (RuCo), which simultaneously reduces the thickness of the liner by 33 percent to 2nm, produces better surface properties for void-free copper reflow, and reduces electrical line resistance by up to 25 percent to improve chip performance and power consumption.

今天,Applied公開展示了其最新的IMS(集成材料解決方案),該解決方案將六種不同的技術組合在一個高真空系統中,其中包括行業首次組合的材料,使芯片製造商能夠將銅線縮放到2納米節點及更高。該解決方案是一種釕和鈷(RuCo)的二元金屬組合,可將襯底厚度同時降低33%至2納米,爲無瑕銅再流動提供更好的表面特性,並將電氣線電阻降低了多達25%以提高芯片性能和能耗。

The new Applied Endura Copper Barrier Seed IMS with Volta Ruthenium CVD* is being adopted by all leading logic chipmakers and began shipping to customers at the 3nm node. An animation of the technology can be viewed here.

新的Applied Endura Copper Barrier Seed IMS with Volta Ruthenium CVD *的技術被所有領先的邏輯芯片製造商採用,並已開始在3nm節點向客戶發貨。這裏可以查看技術的動畫。

Customer Comments

客戶評論

"While advances in patterning are driving continued device scaling, critical challenges remain in other areas including interconnect wiring resistance, capacitance and reliability," said Sunjung Kim, VP & Head of Foundry Development Team at Samsung Electronics. "To help overcome these challenges, Samsung is adopting multiple materials engineering innovations that extend the benefits of scaling to the most advanced nodes."

三星電子排Foundry開發團隊副總裁Sunjung Kim表示:“雖然圖案製作方面的進展推動了持續的器件縮放,但在互連線電阻、電容和可靠性等其他領域仍存在關鍵挑戰。爲了幫助克服這些挑戰,三星正在採用多種材料工程創新,將縮放的好處擴展到最先進的節點。”

"The semiconductor industry must deliver dramatic improvements in energy-efficient performance to enable sustainable growth in AI computing," said Dr. Y.J. Mii, Executive Vice President and Co-Chief Operating Officer at TSMC. "New materials that reduce interconnect resistance will play an important role in the semiconductor industry, alongside other innovations to improve overall system performance and power."

台積電執行副總裁兼共同COO Dr. Y.J. Mii表示:“半導體行業必須提供能源效率性能的顯著提高,以實現人工智能計算的可持續增長。減少互連電阻的新材料將在半導體行業中發揮重要作用,同時還有其他創新措施來提高整體系統性能和功率。”

A Growing Wiring Opportunity

即將到來的佈線機遇

Applied is the industry leader in chip wiring process technologies. From the 7nm node to the 3nm node, interconnect wiring steps have approximately tripled, increasing Applied's served available market opportunity in wiring by more than $1 billion per 100,000 wafer starts per month (100K WSPM) of greenfield capacity, to approximately $6 billion. Looking ahead, the introduction of backside power delivery is expected to increase Applied's wiring opportunity by another $1 billion per 100K WSPM, to approximately $7 billion.

Applied是芯片連線工藝技術領域的行業領導者。從7nm節點到3nm節點,連線工藝步驟大約增加了三倍,使Applied在芯片連線方面的市場可獲得機會每10萬張晶圓每月(10萬WSPM)的綠地產能可增加10億美元,增加至約60億美元。展望未來,預計背面功率傳遞的推出將使Applied的連線機會再增加10億美元每10萬WSPm,增至約70億美元。

The new chip wiring products, along with other materials engineering innovations for making future AI chips, will be discussed at Applied's SEMICON West 2024 Technology Breakfast. The presentation and other materials from the event will be available on the Applied Materials website at: on Tuesday, July 9, 2024 at approximately 9:00 a.m. ET / 6:00 a.m. PT.

新的芯片連線產品以及用於製造未來人工智能芯片的其他材料工程創新技術,將在2024年Applied的SEMICON West技術早餐會上討論。 活動的演示文稿和其他材料將在2024年7月9日星期二上午9:00 Et / 6:00 Pt左右在Applied Materials網站上提供。

*PECVD = Plasma-Enhanced Chemical Vapor Deposition

*CVD = Chemical Vapor Deposition

*PECVD = 等離子增強化學氣相沉積

*CVD = 化學氣相沉積

Forward-Looking Statements

This press release contains forward-looking statements, including those regarding anticipated benefits of our new products and technologies, expected growth and trends in our businesses and markets, industry outlooks and demand drivers, technology transitions, and other statements that are not historical facts. These statements and their underlying assumptions are subject to risks and uncertainties and are not guarantees of future performance. Factors that could cause actual results to differ materially from those expressed or implied by such statements include, without limitation: failure to realize anticipated benefits of our new products and technologies; the level of demand for semiconductors and for our products and technologies; customers' technology and capacity requirements; the introduction of new and innovative technologies, and the timing of technology transitions; market acceptance of existing and newly developed products; the ability to obtain and protect intellectual property rights in technologies; our ability to ensure compliance with applicable law, rules and regulations; and other risks and uncertainties described in our SEC filings, including our recent Forms 10-Q and 8-K. All forward-looking statements are based on management's current estimates, projections and assumptions, and we assume no obligation to update them.

前瞻性聲明

本新聞稿包含前瞻性聲明,包括有關我們新產品和技術的預期益處,我們業務和市場的預期增長和趨勢,行業前景和需求驅動因素,技術轉變以及其他非歷史事實的聲明。這些聲明及其潛在假設受到風險和不確定性的影響,並不保證未來業績。導致實際結果與此類聲明所表達或暗示的結果不同的因素包括但不限於:未能實現我們新產品和技術的預期益處;對半導體和我們的產品和技術的需求水平;客戶的技術和產能要求;引入新的和創新的技術以及技術轉變的時機;市場對現有和新開發產品的接受程度;在技術上取得和保護技術方面的知識產權;我們確保遵守適用法律、法規和規章制度的能力;以及我們在SEC申報中描述的其他風險和不確定性,包括我們最近的10-Q和8-k表格。所有前瞻性聲明都基於管理層的當前估計、投射和假設,並且我們不承擔更新它們的義務。

About Applied Materials

Applied Materials, Inc. (Nasdaq: AMAT) is the leader in materials engineering solutions used to produce virtually every new chip and advanced display in the world. Our expertise in modifying materials at atomic levels and on an industrial scale enables customers to transform possibilities into reality. At Applied Materials, our innovations make possible a better future. Learn more at .

關於應用材料

應用材料公司(納斯達克:AMAT)是世界上幾乎所有新芯片和先進顯示技術的材料工程解決方案的領導者。我們的專業知識使客戶能夠將材料在原子層面和工業規模上進行改性,從而將可能轉化爲現實。在應用材料公司,我們的創新使更美好的未來成爲可能。了解更多信息。

Applied Materials Contact:

Ricky Gradwohl (editorial/media) 408.235.4676

Michael Sullivan (financial community) 408.986.7977

應用材料聯繫人:

Ricky Gradwohl(編輯/媒體)408.235.4676

Michael Sullivan(金融界)408.986.7977

Photos accompanying this announcement are available at

附帶的照片可在以下網址獲取

Applied Materials' Latest Integrated Materials Solution Extends Copper Wiring to 2nm and Beyond

應用材料的最新集成材料解決方案將銅線延伸到2納米及以上

Applied Materials' new Endura Copper Barrier Seed IMS with Volta Ruthenium CVD combines six different technologies in one high-vacuum system, including an industry-first combination of materials that enables chipmakers to scale copper wiring to the 2nm node and beyond.

應用材料的新Endura Copper Barrier Seed IMS與Volta Ruthenium CVD在一個高真空系統中結合了六種不同的技術,包括行業首次組合的材料,使芯片製造商能夠將銅線縮放到2納米及以上。

Combining Ruthenium and Cobalt Improves Chip Performance and Power Consumption

組合釕和鈷可以提高芯片性能和降低功耗

With the semiconductor industry's first use of ruthenium in high-volume production, Applied Materials' new binary metal combination of ruthenium and cobalt (RuCo) enables copper chip wiring to be scaled to the 2nm node and beyond and reduces electrical line resistance by as much as 25 percent.

在半導體行業首次使用釕進行高產量生產,應用材料的新二元金屬組合釕和鈷(RuCo)使得銅芯片線縮放到2納米及以上,並將電器線電阻降低高達25%。

Enhanced Black Diamond Reduces Interconnect Resistance and Strengthens Chips for 3D Stacking

增強型黑色金剛石可以減小互連電阻並強化3D堆疊芯片

Applied Materials today introduced an enhanced version of the company's Producer Black Diamond PECVD dielectric film. This new material enables chip scaling to 2nm and below, while offering increased mechanical strength to help take 3D logic and memory stacking to new heights.

應用材料今天推出了公司的Producer Black Diamond PECVD介電薄膜的升級版。這種新材料可以在提供更大機械強度的同時,將芯片縮放到2納米及以下,以促進3D邏輯和內存堆疊技術的發展。

Source: Applied Materials, Inc.

資料來源:應用材料公司